# Efficiency Improvement of a Chip-Size Antenna for Wireless Microsystems Using Bulk-Micromachining Technology

P. M. Mendes, D. A. Durães, M. Bartek\* and J. H. Correia

Dept. of Industrial Electronics, University of Minho

\*TUDelft/DIMES, The Netherlands

Phone: +351510190, Fax: +351510189, E-mail:paulo.mendes@dei.uminho.pt

**Summary:** This work reports on the use of bulk-micromachining technology to increase the efficiency of a folded shorted-patch antenna. This antenna was designed on two stacked wafers (glass bonded on high-resistivity silicon). The analysis was carried out using the HFSS FEM tool. It was shown that bulk-micromachining technology could be used together with HRS to increase the antenna efficiency by ~20 %. Also, it can be used to allow the use of low-resistivity silicon for antenna substrate. Furthermore, bulk-micromachining technology can be used as an option to tune or to select the antenna operating frequency.

**Keywords:** Bulk-micromachining technology, chip-size antenna

Category: 3

#### 1. Introduction

A topic of growing interest is the concept of integrated antenna. Together with inductances, the onchip antenna integration can be an added benefit in order to achieve a totally integrated RF microsystem. The antenna can be integrated if designed in an IC compatible substrate material. Patch antennas on high-resistivity silicon (HRS) or on glass are possible options [1, 2]. Concerning the antenna efficiency, the glass substrate is better, but the silicon substrate is desirable as it provides a way to directly integrate the RF circuitry. The problem of using HRS is the observed high losses, providing an antenna with low radiation efficiency [3]. To increase the patch antenna efficiency it has been proposed to use bulkmicromachining technology to remove selectively silicon underneath the antenna. Since removing the silicon underneath the patch leads to a larger antenna, a folded shorted-patch antenna can be used instead. This antenna can be built using two-stacked glass wafers [4], or with the bottom wafer substituted by HRS. In this stack the silicon has much higher losses than the glass. The solution is to remove the silicon underneath the middle patch to reduce the losses.

## 2. Fabrication

Bulk micromachining technology is used to selectively remove significant amounts of silicon from a substrate. A silicon nitride membrane is previously deposited in order to serve as etch-stop mask

The bulk-micromachining setup is composed by a etch vessel connected to a thermostatic bath for temperature maintenance at 90°C. The silicon wafer is etched with an aqueous KOH solution (1.5 Kg of KOH in 3 liters of water). The vessel is placed on the top of a magnetic stirrer with a magnet placed inside the vessel to stir the solution. The silicon wafer is mounted face down on an O-ring holder and is suspend inside the KOH bath. Keeping the temperature in the vessel at 85° C, the silicon etch rate is 1.4 µm per minute.

Fig. 1. Bulk-micromachining setup.

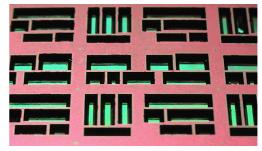

Fig. 2 shows the backside of a silicon wafer etched with an aqueous KOH solution. A silicon nitride membrane was used as etch-stop mask.

Fig. 2. The backside of a silicon wafer etched with an aqueous KOH solution.

# 3. Antenna design and analysis

The cross-section of the proposed antenna structure is presented in Fig. 3. It is built with a glass wafer on the top of a HRS wafer. This structure is favorable for size reduction and at the same time offers the possibility to have circuitry placed in the HRS wafer. The problem of increased losses should now be reduced with the use of bulk micromachining. This will partially remove the silicon underneath the middle patch.

Fig. 3. Cross-section of the micromachined folded patch.

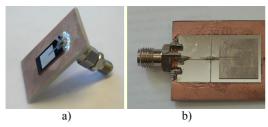

The following analysis was carried out with a model built in HFSS 8.5. This tool was previously used for successful patch antenna design (Fig. 4) on HRS and glass substrates [1-4].

Fig. 4. Patch antennas: a) on HRS; b) on glass.

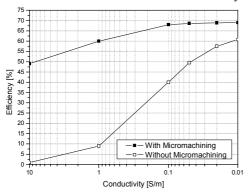

Fig. 5 shows the added benefit of using micromachining for different values of silicon electrical resistivity. When the silicon is completely removed underneath the middle patch, the use of low-resistivity silicon together with micromachining is enough to obtain an antenna with ~50 % efficiency. Moreover, the use of micromachining can always have a benefit of ~10-20 % increase in efficiency.

Fig. 5. Efficiency vs. conductivity for  $d = 500 \mu m$ .

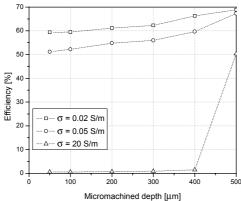

Fig. 6 shows the effect on efficiency for different micromachined depths. As expected, the efficiency rises when the depth of the removed silicon is increased. Also, it is clearly shown the effectiveness of micromachining to enable the use of low-resistivity silicon as antenna substrate.

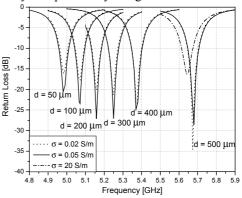

The Fig. 7 presents the return loss for different micromachined depths, when all the other dimensions are kept unchanged. As it can be observed, the drawback is the shift of the operating frequency for higher frequencies when the micromachined depth increases.

Fig. 6. Efficiency vs. micromachined depth.

This leads to larger antennas when using micromachining. On the other hand, we can take advantage of this effect. It can be used as a post-processing step to change, or to tune, the operating frequency of a previously designed antenna.

Fig. 7. Return loss for different micromachining depths.

# 4. Conclusions

This work shows how silicon bulk-micromachining technology can be used to increase the efficiency of a folded shorted-patch antenna. Also, it can be used as an option to tune or to change the antenna operating frequency. The use of bulk-micromachining technology allows the increase of the antenna efficiency approximately 20 %. It was also observed that the use of bulk-micromachining technology to etch completely the silicon wafer underneath the antenna allows to use regular silicon wafers instead of HRS wafers.

## 5. Acknowledgements

The authors would like to thanks the Portuguese Foundation for Science and Technology for funding this work (SFRH/BD/4717/2001 and POCTI / ESE / 38468 / 2001).

### References

[1] P. M. Mendes, M. Bartek, J. N. Burghartz, J. H. Correia, "Design and Analysis of a 6 GHz Chip Antenna on Glass Substrates for Integration with RF/Wireless Microsystems", to be presented at IEEE APS Int. Symp., Columbus, Ohio, USA, June 22-27, 2003

[2] P. M. Mendes, M. Bartek, J. N. Burghartz, J. H. Correia, "Design and Tolerance Analysis of a 5.7 GHz Chip-Size Microstrip Antenna on High Resistivity Silicon", to be presented at URSI-B, Columbus, Ohio, USA, June 22-27, 2003.

[3] P. M. Mendes, J.H. Correia, M. Bartek, J.N. Burghartz, "Analysis of Chip-Size Antennas on Lossy Substrates for Short-Range Wireless Micro Systems", Proc. SAFE 2002, 8, Veldhoven, The Netherlands, pp. 51-54, November, 2002.

[4] P. M. Mendes, A. Polyakov, M. Bartek, J. N. Burghartz, J. H. Correia, "Integrated 5.7 GHz Chip-Size Antenna for Wireless Sensor Networks", to be presented at Transducers'03, Boston, USA, June 8-12, 2003.