Introducevi:

lonceitos basisios:

$$E = h V = h W$$

$h = 6626 \times 10^{-34} J.s$

$h = -\frac{h}{2\pi}$

$h = 1.055 \times 10^{-34} J.s$

$h = 1.055 \times 10^{-34} J.s$

$m_{olechnei} = 9.409 \times 10^{-34} Kg.$

$M_{olechnei} = 9.409 \times 10^{-34} Kg.$

$Kg = 8.617 \times 10^{-5} eV K^{-1}$

Marson do electrais no Gristal ema preserva de E

$m_{e}^{H} = \frac{R^{2}}{d^{2}E} = \frac{1}{2} massa efectiva}$

$\frac{d^{2}E}{dK^{2}}$  O electreais livre mais imbrae

$dK^{2}$  Corr a rede e mit me

A massa efectiva adrem da interargais do

electros com a rede devido a compos oléctrico:

$$\widehat{}$$

Semicondutores Estrutura aistalina e hijagoès Semicondutores do grupo IV (Si, Ge, C,...) Base (motivo): 2 átomos (C, Ge, Si,...) donticos fiçaçãos: covalente - 2 electracões (11) partilhados por 2 atomos  $E_X: Si(1s^2, 2s^2, 2b^6, 3s^3b^2)$ Cada étomo de Si (ligado a outros 4) Contribui con un electros para ligaços (dupla) Servicondutores do guyo III-II - contern un demento do guyo III, outro do gupo I (GaP, Im As, GaSb, Ga As). Si As Care Si Si A s Ď As Rede cúbico de faces Centradas

Condutividade Eléctrica nos semicondutores: tipo-m. Volory tipicos n= 10<sup>15</sup> cm<sup>-3</sup> ( 10<sup>21</sup> cm<sup>-3</sup>)  $G_e = 10^{-12}$  $M_e^* = 0.1 m_0$ f=1  $2m^{-1}$ Num metal:  $n = 10^{28} \text{m}^{-3} = 5 = 10^{+1} \text{m}^{-1}$ Mobilidade: rozos entre a Vé, véhoidade dos déchés e a interridade de compo Éaplicado é a predida da failidade con que o electeri remove na presença de un É.  $\mu = \frac{V_e}{E}$   $e V_e = -\frac{e}{m_e^*} \frac{E}{E} = 2/\mu_e = \frac{e}{m_e^*} \frac{E}{m_e^*}$ eliminando de en / mil= re= e de mé Jo=ne<sup>2</sup> Te me  $\mathcal{G}_{e} = \mathcal{M}_{e} | \mathcal{M}_{e} | = \mathcal{M}_{e} \mathcal{M}_{e}$  para baimon.  $\mathcal{G}_{h} = \mathfrak{p} \cdot e | \mathcal{M}_{h} | = \mathfrak{m} \cdot e | \mathcal{M}_{e}$

SEMICONDUTORES DE GAP DIRECTO E INDILECTO Transiças de clectrons da B.V. para B.C. de-je por absorian de uma ou mais fotoes A frequencia V do fotat tem de jer  $V \ge \frac{\Delta E}{R}$ 6 processo passa-se con conservação da energia e da quantidade de movimento. Regna de seleccars: so son possíveis transições vahicais (per variagans de K) entre a B.V. a B.C. e awrite e mos jernicondutions de gap directo. As Ga E GAP Directo Si E E GAP invoinecto B.C. k 1.08eV k B.V. 6 fondo da B.C. Mão se ancontra directamente or baixo do topo da B.V. A transicañ o corre em pansos: i) o electria absorve un Fotaio e un formas fotão ponnece a evenção necessária e o forao a pontidade de movimento (= 0.05eV). 12.

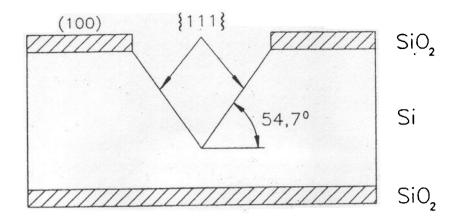

Fig. 2.7 Profile of an etched trench in (100)-silicon

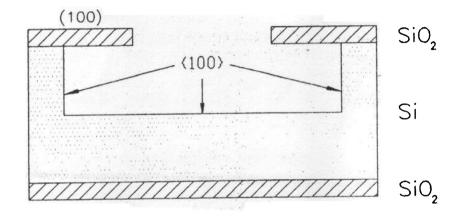

Fig. 2.8 Trenches with vertical walls in (100)-silicon

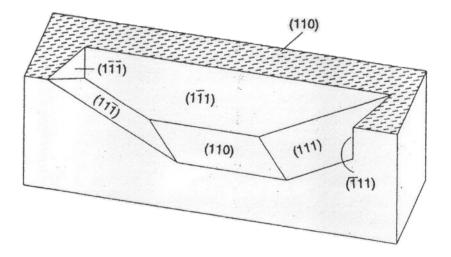

Fig. 2.9 Shapes of etched deepings in (110)-silicon

CMOS PROCESS TECHNOLOGY Process Features

The CMOS01 process is a 1.6 µm Poly Silicon gate CMOS technology. It uses a 12 µm p-type epi layer on four inch low ohmic p-type substrate wafers. The nchannel device is made directly in the epi and the p-channel device is made in an N-well. For the n-channel devices precautions are taken (Ldd implants) to prevent hot electron gate oxide degradation mechanisms.

#### Some further characteristics:

| Single Poly                                       |   |               |

|---------------------------------------------------|---|---------------|

| Double Metal                                      |   |               |

| Gate Oxide Thickness                              | : | 25 nm         |

| Minimum Gate Length                               | : | 1.6 µm        |

| Minimum Pitch for Metal 1 and Metal 2             | : | 4.8 µm        |

| Minimum Pitch for Poly Silicon                    | : | 4.0 µm        |

| Nominal Supply Voltage                            | : | 5.0 V         |

| Maximum Ratings                                   | : | -0.5 to 6.5 V |

| MOS Transistors W/L=20/1.6 @ 27 °C                |   |               |

| Threshold Voltages, typical values                |   |               |

| Vt_n                                              |   | 0.75 V        |

| Vt_p                                              | : | -1.10 V       |

| Saturation Currents @IVdsl=5V, IVgsl=5V, IVbsl=0V |   |               |

| Ids,sat_n                                         | : | 4.75 mA       |

| Ids,sat_p                                         | : | 1.90 mA       |

|                                                   |   |               |

## Process Flow

The CMOS01 process is a conventional CMOS process, based on LOCOS. In the following cross sections the process flow is shown for the construction of a basic CMOS inverter, if the masks NW, OD, NWI, PS, SP, SN, CO, IN, COS and INS are applied. For a detailed definition of these mask names see chapter 4.

#### Short desription of the subsequent process steps:

The starting material is a p-type substrate with a 12  $\mu$ m epitaxial layer.

A 660 nm thick oxide is grown and NW areas are defined. Phosphor is implanted and the masking oxide layer is removed. Now the pad oxide stack, consisting of 40 nm oxide and 100 nm nitride is defined by the OD mask.

Before growing the LOCOS oxide an NWI mask is applied. The NW region is masked by both the pad oxide stack and the photoresist layer and this is thick enough to protect the NW for the two following boron implantations. The first one with low energy is the (parasitic) channel stopper, which is only present outside the pad oxide stacks. The second implantation with high energy is the n-channel anti punch through implant. Due to its high energy the boron implant can cross the pad oxide stack.

Now the LOCOS oxide is grown and the pad oxide is removed. A 25 nm gateoxide is grown followed by a boron threshold adjust implant. Now poly silicon is deposited, which is made low ohmic by phosphorous doping and the transistor gates, poly silicon resistors and poly tracks are defined by the PS mask. The SN mask is applied and a phosphor implantation forms the ODN+ areas for the source or drain of n-channel MOSTs and N+ resistors. A gate spacer technology is used consisting of a deposited TEOS oxide layer, which enables the formation of a so called D(ouble)D(iffused)D(rain) or L(igthly)DD. The SN mask is applied again and the second implant is arsenic. Now the SP mask is applied and boron is implantated, which forms the ODP+ areas for the source or drain of p-channel MOSTs and P+ resistors.

The previous steps are defined as front-end processing and all the semiconductor devices are made. What rests is 'just' the connection between them and to the outside world. The following steps are called back-end processing.

A 100nm TEOS layer and a 600nm B(oron)P(hosphor)S(ilicate)G(lass) layer are deposited. The latter is reflowed to planarize the topology. The CO mask is applied and contact windows are etched to reach ODN+, ODP+ and PS regions. The wafer is covered with aluminium and the IN mask defines the first interconnect layer. Then plasma oxide is deposited, which serves as insulating layer. The COS mask is applied and contact windows are etched. The wafer is coverd again with aluminium and the INS mask is applied to define the second interconnect layer. On request the last step in the process can be the deposition of a scratch protection layer, which requires the CB mask for definition of the contact openings to the bondpads.

# Devices Device Types

The following devices are available in the CMOS01 process :

#### Transistors

n-channel enhancement MOS transistor p-channel enhancement MOS transistor vertical pnp transistor (poor man's bipolar)

#### **Diodes**

n+/p- junction diode (ODN+/SUB) p+/n- junction diode (ODP+/NW) n-/p- junction diode (NW/SUB)

#### **Resistors/Conductors**

Poly Silicon resistor (PS) Diffused resistors (ODN+ and ODP+) N-Well resistors (NW) First metal resistor (IN) Second metal resistor (INS)

#### Capacitors

IN-PS plate capacitor INS-IN plate capacitor INS/PS - IN sandwich plate capacitor PS-ODN+ capacitor

Other resistors and capacitors should not be used. They are just parasitic elements, which are not explicitly monitored and have values that can change due to process variation.

-----

#### **Mask Names**

The following mask names are reserved and can not be used for other purposes than indicated.

Coding masks for the circuit designer to use:

- NW N-Well definition

- OD Oxide Definition for creating active area

- PS Poly Silicon definition

- SP Shallow P, P+ implantation definition

- SN Shallow N, N+ implantation definition

- CO COntact window definition of IN to OD or IN to PS

- IN INterconnect definition of first metal layer

- COS COntact window Second, definition of via from INS to IN

- INS INterconnect Second, definition of second metal layer

- CB Contact window Bondpad, definition of scratch protection openings

Additionally the following "software" masks can be specified to

explicitly define the functionality of the layers underneath:

This may be useful for layout extraction programs.

- GRN Guard Ring N, NW/N+ definition

- GRP Guard Ring P, P+ definition

- **RNW** Resistor NW definition

- RPD Resistor Poly or OD definition

Physical masks, used for mask making:

NW, OD, NWI (\*), PS, SP, SN, CO (\*\*), IN, COS, INS, CB.

- (\*) Inverse NW mask. Necessary because only one type photoresist is used.

- (\*\*) Note that the CO mask can be a merged mask from the three different

contact types CON, COP and CPS as specified below.

- CON Contact hole for connection of IN with ODN+

- COP Contact hole for connection of IN with ODP+

- CPS Contact hole for connection of IN with polysilicon

#### Mask Numbering

In general the following convention is used for the numbering of the masks in a Gds2 output layer file

1

| Gds2 number: | in use for:             |

|--------------|-------------------------|

| 0-40         | masks                   |

| 41-51        | plottext, pattern frame |

| 52-62        | for special use         |

| 63           | bulk                    |

#### Definition of mask numbering in Gds2 for the DIMOS01 process:

| Gds2 mask name | Gds2 mask number | inverted y/n | total grow[µm] |

|----------------|------------------|--------------|----------------|

| NW 11.         | 10               | n            | 0              |

| OD (200.       | 7                | у            | 1.2            |

| NWI            | 10               | y            | 0              |

| PS -           | 3                | y            | 0.30           |

| SN             | 6                | n            | 0              |

| SP Inri        | 9                | n            | 0              |

| CO , ' · · ·   | 11               | n            | 0              |

| IN ·           | 2                | у            | 0              |

| COS            | 21               | n            | 0              |

| INS - ("1":"   | 22               | y            | 0              |

| CB             | 16               | n            | 0              |

| CON            | 31               | n            | 0              |

| COP            | 32               | n            | 0              |

| CPS            | 33               | n            | 0              |

| RPD            | 35               | n            | 0              |

| RNW            | 36               | n            | 0              |

| GRN            | 38               | n            | 0              |

| GRP            | 39               | n            | 0              |

There are special mask layers, e.g. plottexts, which are not used for making physical masks.

| Gds2 mask name | Gds2 mask number | in use for:              |

|----------------|------------------|--------------------------|

| PTODN          | 41               | plottext attached to OD  |

| PTPS           | 42               | plottext attached to PS  |

| PTIN           | 43               | plottext attached to IN  |

| PTINS          | 44               | plottext attached to INS |

| BB             | · 40             | Bounding box             |

# 4.3 Layout design rules

#### Definitions used in the layout design rules

| thin oxide                                                                       | - | OD covered with PS.                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OD N <sup>+</sup><br>OD P <sup>+</sup>                                           | - | OD covered with SN.<br>OD covered with SP.                                                                                                                                                                                                  |

| cold N-well<br>hot N-well                                                        | - | N-well connected to the most positive voltage (VDD).<br>N-well not connected to the most positive voltage.                                                                                                                                  |

| cold diffusions :<br>outside the N-well<br>inside the N-well                     | - | a diffusion which has the same potential as the substrate.<br>a diffusion which has the same potential as the N-wel                                                                                                                         |

| hot diffusions :<br>hot N <sup>+</sup> diffusion<br>hot P <sup>+</sup> diffusion | - | all N <sup>+</sup> diffusion regions outside the N-well which have a<br>potential not equal to the substrate voltage<br>all P <sup>+</sup> diffusion regions inside the N-well which have a<br>potential not equal to the N-well potential. |

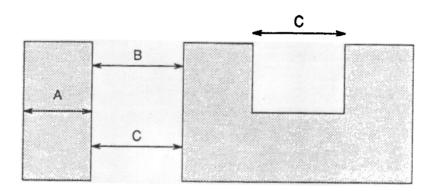

#### Terminology and numbering used in the layout design rules

- 0. general rule without specification of geometry in  $\mu$ m.

- 1. width or dimension of A

- 2. space between two regions of A

- 3. overlap of B over A (in all directions)

- 4. separation from A to B

• •

- 5. extension of A edge beyond B edge (in 1 or more directions)

- 6. extension of A region inside B region (in 1 or more directions)

- 7. rule for the specified layer, concerning other masks

Note: All specified geometries must be interpreted as Dimensions On Silicon.

1

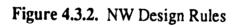

### Level : NW - N-Well

| NW.1.1    | The dimensions of NW are determined by other rules, however the minimum dimensions are | А | 8.0 µm  |

|-----------|----------------------------------------------------------------------------------------|---|---------|

| NW.2.1    | Minimum space between two NW regions                                                   | А | 0.0 µm  |

| 14 44.2.1 |                                                                                        |   |         |

|           | with at least one not connected to VDD (hot well)                                      | В | 12.8 µm |

| NW.2.2    | Minimum space between two NW regions,                                                  |   |         |

|           | both connected to VDD (cold wells)                                                     | С | 8.0 µm  |

|           | · · ·                                                                                  | C | οινμπ   |

|           | Merge if spacing is less.                                                              |   |         |

1

- -

. **her**\_\_\_\_

#### Level : OD - Oxide Definition

| OD.0.1 | OD areas have to be covered with either SN or SP (see SN and SP rules                  | s) |        |

|--------|----------------------------------------------------------------------------------------|----|--------|

| OD.1.1 | Minimum OD width for interconnect                                                      | Α  | 1.6 µm |

| OD.2.1 | Minimum space between two OD regions<br>(both regions are inside or outside an N-well) | ·B | 3.2 µm |

| OD.3.1 | Minimum NW overlap over OD P+                                                          | С  | 4.8 µm |

| OD.3.2 | Minimum NW overlap over OD N+ (N-well contact)                                         | С  | 0.0 µm |

| OD.4.1 | Minimum separation from OD N+ to a cold N-well                                         | D  | 4.8 µm |

| OD.4.2 | Minimum separation from OD N+ to a hot N-well                                          | D  | 9.6 µm |

| OD.4.3 | Minimum separation from OD P+ to NW (substrate contact)                                | E  | 4.8 µm |

Figure 4.3.3. OD Design Rules